集成電路設計 現代電子科技的基石與創新引擎

在當今這個高度數字化的時代,集成電路(IC)已經滲透到我們生活的方方面面,從智能手機、個人電腦到智能家居、汽車電子,再到數據中心和人工智能系統,其無處不在的身影正悄然推動著社會的前進。而這一切的核心驅動力,正是集成電路設計這一高科技領域的持續創新與突破。

集成電路設計,簡而言之,就是將數百萬乃至數十億個晶體管、電阻、電容等電子元件,通過精密的布局與連線,集成在一塊微小的硅片上,以實現特定的復雜功能。它并非簡單的物理堆疊,而是一個融合了物理學、材料科學、電子工程、計算機科學和數學等多學科知識的系統性創造過程。

設計流程:從概念到芯片的精密旅程

一個集成電路的誕生,通常始于一個明確的市場需求或一個創新的技術構想。整個設計流程可以概括為以下幾個關鍵階段:

- 系統架構與規格定義:明確芯片需要實現的功能、性能指標(如速度、功耗、面積)、工作環境以及成本目標。這是設計的“藍圖”階段。

- 前端設計(邏輯設計):設計工程師使用硬件描述語言(如Verilog或VHDL)將架構轉化為寄存器傳輸級(RTL)代碼,描述電路的數字邏輯行為。隨后進行功能仿真與驗證,確保邏輯正確。

- 后端設計(物理設計):這是將RTL代碼“翻譯”成實際物理版圖的過程。包括邏輯綜合(將RTL轉換為門級網表)、布局(確定每個元件在芯片上的位置)、布線(連接所有元件)、時序分析、功耗分析以及物理驗證等。此階段直接決定了芯片的最終性能、可靠性和制造成本。

- 制造與封測:將設計完成的版圖數據(GDSII文件)交付給晶圓代工廠(Foundry)進行光刻、刻蝕、摻雜等工藝制造,形成晶圓。之后進行切割、封裝成獨立芯片,并進行嚴格的測試,確保良率與功能達標。

核心挑戰與關鍵技術

隨著工藝節點不斷微縮至納米級(如5nm、3nm甚至更小),集成電路設計面臨著前所未有的挑戰:

- 功耗與散熱:晶體管密度飆升導致功耗密度激增,“功耗墻”問題日益突出。低功耗設計技術,如多閾值電壓、電源門控、動態電壓頻率調整等,變得至關重要。

- 時序收斂與信號完整性:在高頻下,互連線延遲、串擾、電源噪聲等問題嚴重影響信號質量與時序。

- 設計與制造協同(DTCO):設計師必須深入理解先進工藝的物理限制(如光刻限制、器件變異),在設計中提前規避制造風險。

- 設計復雜度與成本:超大規模集成電路的設計周期長、投入巨大,需要高度自動化的電子設計自動化工具鏈支撐。

為了應對這些挑戰,一系列創新設計方法和技術應運而生:

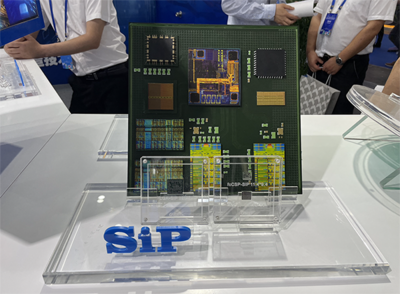

- 異構集成與Chiplet(芯粒)技術:不再追求將所有功能集成于單一巨型芯片,而是將不同工藝、不同功能的芯粒通過先進封裝(如2.5D/3D IC)集成在一起,實現性能、成本與開發周期的優化。

- 基于AI/ML的設計自動化:利用機器學習優化布局布線、功耗預測、良率提升等,大幅提升設計效率與質量。

- 特定領域架構:針對人工智能、自動駕駛、高性能計算等特定應用,設計高度定制化的專用集成電路,在能效比上遠超通用處理器。

未來展望

集成電路設計將繼續沿著“更智能、更高效、更集成”的方向演進。隨著新材料(如二維材料)、新器件(如環柵晶體管GAA)、新計算范式(如存算一體、量子計算)的探索,設計方法論也將發生深刻變革。開源硬件(如RISC-V指令集架構)的興起,正降低設計門檻,推動產業生態的多元化與創新活力。

總而言之,集成電路設計是連接創新思想與物理實現的橋梁,是信息產業皇冠上的明珠。它不僅是一門精密的工程技術,更是一門充滿藝術性的創造學問。對于有志于投身這一領域的工程師和研究者而言,它意味著無限的挑戰與機遇,是塑造未來智能世界的核心力量。

如若轉載,請注明出處:http://m.aozhang.cn/product/58.html

更新時間:2026-01-06 08:52:31